# Texts in Computer Science

Editors

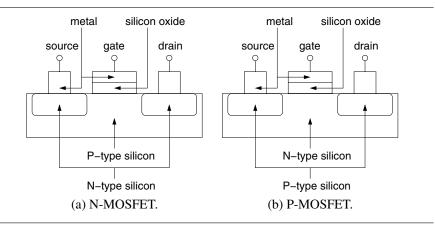

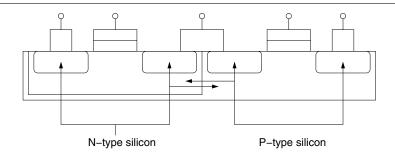

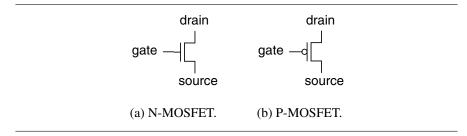

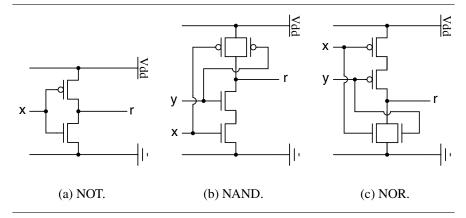

David Gries

Fred B. Schneider

For further volumes: http://www.springer.com/series/3191

# A Practical Introduction to Computer Architecture

Dr. Daniel Page University of Bristol Dept. Computer Science Room 3.10, Merchant Venturers Building Woodland Road, Bristol United Kingdom, BS8 1UB page@compsci.bristol.ac.uk

Series Editors

David Gries

Department of Computer Science

Upson Hall

Cornell University

Ithaca, NY 14853-7501, USA

Fred B. Schneider Department of Computer Science Upson Hall Cornell University Ithaca, NY 14853-7501, USA

ISBN 978-1-84882-255-9 e-ISBN 978-1-84882-256-6 DOI 10.1007/978-1-84882-256-6 Springer Dordrecht Heidelberg London New York

British Library Cataloguing in Publication Data A catalogue record for this book is available from the British Library

Library of Congress Control Number: 2009922086

#### © Springer-Verlag London Limited 2009

Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms of licenses issued by the Copyright Licensing Agency. Enquiries concerning reproduction outside those terms should be sent to the publishers.

The use of registered names, trademarks, etc., in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant laws and regulations and therefore free for general use.

The publisher makes no representation, express or implied, with regard to the accuracy of the information contained in this book and cannot accept any legal responsibility or liability for any errors or omissions that may be made.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# **Foreword**

It is a great pleasure to write a preface to this book. In my view, the content is unique in that it blends traditional teaching approaches with the use of mathematics and a mainstream Hardware Design Language (HDL) as formalisms to describe key concepts. The book keeps the "machine" separate from the "application" by strictly following a bottom-up approach: it starts with transistors and logic gates and only introduces assembly language programs once their execution by a processor is clearly defined.

Using a HDL, Verilog in this case, rather than static circuit diagrams is a big deviation from traditional books on computer architecture. Static circuit diagrams cannot be explored in a hands-on way like the corresponding Verilog model can. In order to understand why I consider this shift so important, one must consider how computer architecture, a subject that has been studied for more than 50 years, has evolved.

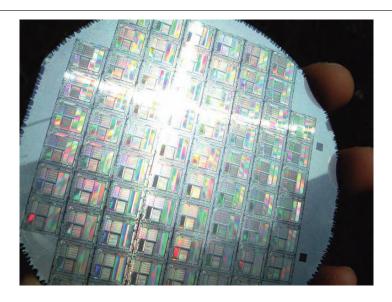

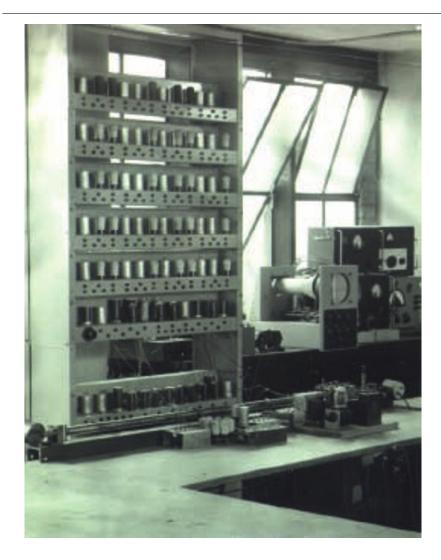

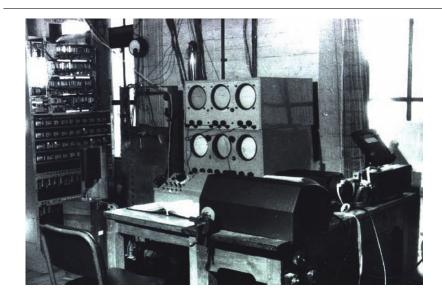

In the pioneering days computers were constructed by hand. An entire computer could (just about) be described by drawing a circuit diagram. Initially, such diagrams consisted mostly of analogue components before later moving toward digital logic gates. The advent of digital electronics led to more complex cells, such as half-adders, flip-flops, and decoders being recognised as useful building blocks. However, miniaturisation of devices and hence computers has led to the design of single circuits containing millions or even billions of components. As a result, hand-lay-out is only used for specific modules, and circuit diagrams are less useful as a mechanism for describing functionality for real circuits.

Instead, two formalisms are used in industry: HDLs and mathematics. A HDL allows us to tell the component-layout and simulation tools how we would like to implement our circuit; mathematics tells us what the circuit ought to do. In order to verify whether the circuit does what we want it to, we can (partly mechanically) compare the mathematical description with the HDL description. This represents increased use of abstraction to cope with complexity, and an engineer can now be productive by simply understanding and using high-level circuit design (e.g., multiplier design or pipelined processors) and formalisms (e.g., HDLs and mathematics).

viii Foreword

Circuit diagrams are still used in the design flow, but mostly to sketch the physical layout, in order to predict whether a circuit can be laid out sensibly.

Dealing with gaps in understanding between such a wide range of concepts and techniques is often off-putting for people new to the subject. The best way to approach the problem is by placing it within a practical context that enables students to experiment with ideas and discover themselves the advantages and disadvantages of a particular technique.

In this book, Dan does just that by giving an excellent overview of key concepts and an introduction to formalisms with which they can be explored. I hope this book will inspire many readers to follow a career in this fascinating subject.

Henk Muller. Principal Technologist, XMOS.

# **Preface**

In theory there is no difference between theory and practice. In practice there is.

- L.P. "Yogi" Berra

### **Overview**

In my (limited) experience, and although there are a number of genuinely excellent textbooks on the subject, two main challenges exist in relation to delivery of University level taught modules in computer architecture:

- 1. Such modules are often regarded as unpopular and irrelevant by students who have not been exposed to the subject before, and who view a computer system from the applications level. This is compounded by the prevalence of technologies such as Java which place a further layer between the student and actual computer hardware. In short, and no matter how one tries to persuade them otherwise, students often see no point in learning about the internals of a computer system because they cannot see the benefit.

- 2. Conventional textbooks teach the subject in a different way than in other modules students are exposed to at the same time. For example, conventional wisdom says that one cannot "teach" programming, one has to "do" programming in order to learn. This is in stark contrast to textbooks on computer architecture where students are often forced to learn in a more theoretical way, learning by taking facts for granted rather than experimenting to arrive at their own conclusions. For example, because of the difficulty in working with large logic designs on paper, any practical work is often limited and hence detached from the more challenging content.

I would argue that this is a shame: computer architecture represents a broad spectrum of fundamental and exciting topics that underpin computer science in general. Aside from the technical challenges and sense of achievement that stem from

x Preface

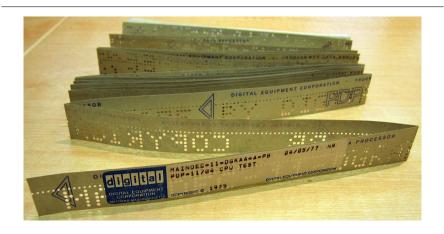

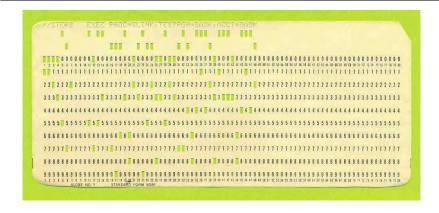

understanding exactly how high-level programs are actually executed on devices built from simple building blocks, historical developments in computer architecture neatly capture and explain many design decisions that have shaped a landscape we now take for granted. The representation of strings in C is a great example: the null-terminated ASCIIZ approach was not adopted for any real reason other than the PDP-7 computer included instructions ideal for processing strings in this form, and yet we still live with this decision years after the PDP-7 became obsolete. Seemingly frivolous anecdotes and examples like this are increasingly being consigned to history whereas from an Engineering perspective, one would like to learn and understand previous approaches so as to potentially improve in the future.

International experts regularly debate tools and techniques for delivering University-level modules in computer architecture; the Workshop on Computer Architecture Education (WCAE), currently held in conjunction with the International Symposium on Computer Architecture (ISCA), is the premier research conference in this area. This book represents an attempt at translating my personal philosophy, that theoretical concepts should be accessible for practical experimentation, into a form suitable for use in such modules. Put simply, I see computer architecture as a subject in which "getting things done" is paramount; the ability to understand tradeoffs before selecting between and implementing well considered design options is often as important as the study of those options at a more theoretical level. This focus is underlined by the book sub-title: a "practical" approach is the aim throughout. To enable this, a key feature of this book is inclusion and use of a hardware description language (i.e., Verilog), and a concrete processor (i.e., MIPS32) as practical vehicles for modelling and experimenting with digital logic and processor design.

# Target Audience

The content is organised into three parts which contain a total of thirteen core chapters. Although some slight disagreement about inclusion of specific topics is inevitable, the chapters represent a compromise between my informal opinion, interests and experience, and more formal curriculum guidelines such as that developed by the UK Quality Assurance Agency (QAA):

Of course, international equivalents exist; examples include those developed jointly by the IEEE and ACM, leading professional bodies within this domain:

```

http://www.computer.org/curriculum/

```

The general aim of this book is to cover topics *every* computer science student should have at least a basic grasp of, and equip said students with enough knowledge to read and understand more advanced textbooks. In this respect, the core target audience is first-year Undergraduate students with a rudimentary knowledge of

Preface xi

programming in C. More generally, the book content is pitched at a level which satisfies most of the demands that have resulted from our degree programmes at the University of Bristol. In particular, the more advanced material has proved useful as a bridge toward, or in support of, more specialised textbooks that cover later-year Undergraduate and Postgraduate modules.

### Organisation

The book chapters are described briefly below. Very roughly the three parts of the book can be viewed as somewhat self-contained, representing three layers or levels of abstraction: the **digital logic layer**, the **instruction set and micro-architecture layer**, and the **hardware/software interface**. Part 1 deals with basic tools and techniques which underpin the rest of the book:

- **Chapter 1** Introduces the theoretical background including logic, sets, and number representation.

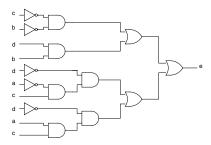

- **Chapter 2** Uses the theory developed in the previous chapter to describe the basics of digital logic including logic gates and their construction using transistors, combinatorial and clocked circuits and their optimisation.

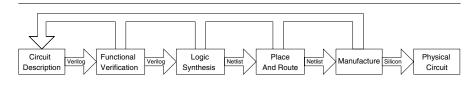

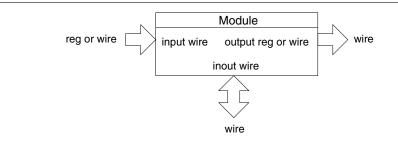

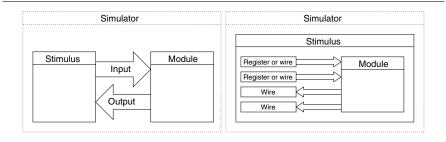

- **Chapter 3** As a means of realising the digital logic designs presented in the previous chapter, Verilog is presented in an introductory manner; this content is written with a reader who is a proficient C programmer in mind.

Part 2 deals with the broad topic of processor design and implementation. The content takes a step-by-step approach, starting with a functional description of a computer processor and gradually expanding on the details, issues and techniques that have resulted in modern, high-performance processor designs:

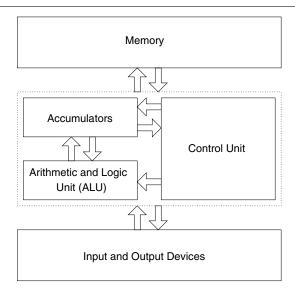

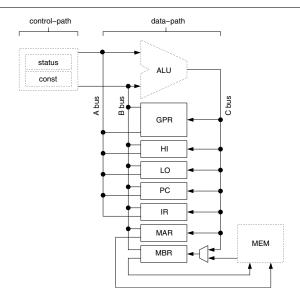

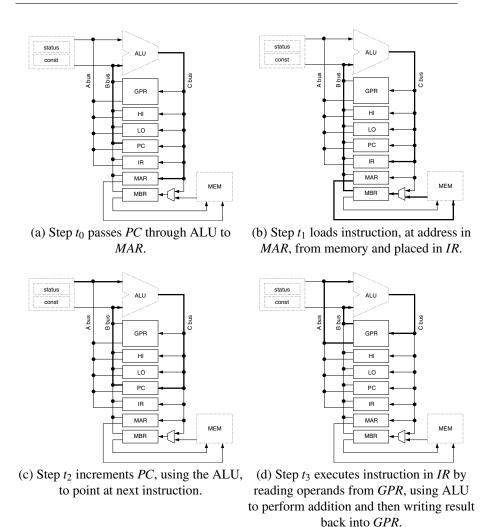

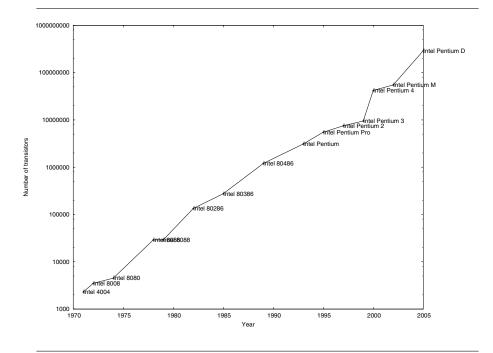

- **Chapter 4** The first step in introducing the design of processors (as an extension to the study of general circuits) is to track historical developments and use them as a means to explain central concepts such as the fetch-decode-execute cycle.

- **Chapter 5** Once the core concepts are introduced, a concrete realisation in the form of MIPS32 is discussed; this discussion includes details such as addressing modes and instruction encoding for example.

- **Chapter 6** This chapter outlines some basic methods for evaluating processors in terms of various metrics which can be used to defined quality, focusing on performance in particular.

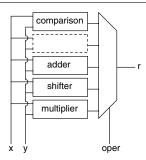

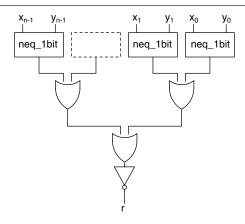

- **Chapter 7** As a vital component in any processor, the design of efficient circuits for arithmetic (e.g., addition and multiplication) is introduced and demonstrated using Verilog.

- **Chapter 8** In the same way as arithmetic, the design of efficient components in the memory hierarchy is introduced and demonstrated using Verilog.

- **Chapter 9** Finally, a number of more advanced topics in processor design are investigated including approaches such as superscalar and vector processors.

xii Preface

Finally, Part 3 attempts to bridge the gap between hardware and software by examining the programming tools and operating system concepts that support the development and execution of programs:

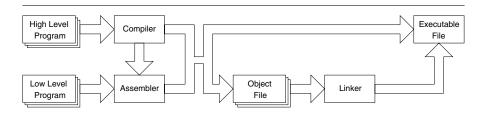

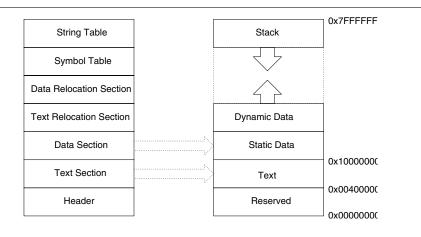

- Chapter 10 As a first step, this chapter presents a detailed description of a development tool-chain, starting with linkers and assemblers. This material is supported by and links to Appendix A, which provides a stand-alone tutorial on using SPIM, a MIPS32 simulator. As such, it provides a concrete means of writing programs for the processor design introduced earlier in the book.

- **Chapter 11** Following the previous chapter, compilers are now introduced by focusing on their aspects which are most closely tied to the processor they target. For example, register allocation, instruction select and scheduling are all covered.

- **Chapter 12** With a means of writing programs established, the operating system layer is introduced in a practical way by using SPIM as a platform for real implementations of concepts such as scheduling and interrupt handling.

- Chapter 13 Finally, a somewhat novel chapter examines the concept of efficient programming. This is written from the point of view of a programmer who wants (or needs) to capitalise on the behaviour and characteristics of the concepts presented in previous chapters to improve their programs.

Each chapter concludes with a set of example questions which are largely at a level one might encounter in a degree-level examination. These questions are numbered consecutively (rather than relative to the chapter number) and a set of example solutions can be found in Appendix B.

Although this content might clearly contain accidental omissions, some topics have been avoided by design. Optimistically, one might view them as ideal for inclusion in future versions of the book; more realistically they represent topics that are important but not vital at the level the book is aimed at:

- Perhaps the largest omission, at least the one which seems likely to prompt the

loudest outcry, is that of floating point arithmetic. Although the book covers

floating point representation briefly, the circuits for arithmetic and instruction

sets that use them are integer only. The rationale for this decision was purely

space: floating point represents a fairly self-contained topic which could be left

out without too negative an impact on core topics covered by the rest of the

content.

- A similar situation exists with the topic of design verification: although testing

the digital logic designs one can produce with Verilog is important, one could

easily dedicate an entire book to the art of good design verification.

- The main emphasis of the book is processors and as such, they are examined somewhat in isolation. This contrasts with reality where such processors typically form part of a larger system including peripherals, communication networks and so on. As such, the broad topic of system-level design, which is central to other books, is not covered here.

- At the time of writing, the "hot topic" in computer architecture is the advent of **multi-core** devices, i.e., many processors on a single chip. Although this has been

Preface xiii

a research area for many years in an attempt to cope with design complexity and effective use of increased transistor counts, commodity multi-core devices have breathed new life into the subject. Again, because the emphasis is more intraprocessor than inter-processor, we omit the topic here although among all the options for future material this is perhaps the most compelling.

• The book covers only traditional logic styles. However, for specific application areas it has become attractive to investigate alternatives; the idea is basically that one should be aware of available alternatives and use the right one in the right place. Specifically, secure logic styles (which help to prevent certain types of passive attack) and asynchronous logic (which avoids the need for global clock signals) represent interesting avenues for future content.

#### Contact

As people who know me will (too) willingly attest, I am far from perfect. As a result, this book is sure to include problems in the shape of minor errors and mistakes. If you find such a problem, or have a more general comment, I would be glad to hear about it; you can contact me via

http://www.cs.bris.ac.uk/home/page/

# Acknowledgements

This book was typeset with LATEX, originally developed by Leslie Lamport and based on TEX by Donald Knuth; the listings package by Carsten Heinz, the algorithm2e package by Christophe Fiorio and karnaugh by Andreas Wieland were all used in addition to the basic system. The various figures and source code listing were generated with the help of ModelSim, a Verilog simulator by Mentor Graphics; GTKWave, a VCD waveform viewer by Anthony Bybell; xfig, a general vector drawing package originally written by Supoj Sutanthavibul and maintained by many others; xcircuit, a circuit vector drawing package by Tim Edwards; asymptote, a scripted vector drawing package by Andy Hammerlindl, John Bowman, and Tom Prince; SPIM, a MIPS32 simulator written by James Larus; Dinero, a cache simulator written by Jan Edler and Mark Hill; and finally gcc the GNU C compiler, originally by Richard Stallman and now maintained by many others.

Throughout the book, images from other sources are reproduced under specific licenses; each image of this type carefully notes the source and the license in question. Specific details of the GNU Free Documentation License and Creative Commons Licenses can be found via

http://www.gnu.org/licenses/

xiv Preface

### http://creativecommons.org/licenses/

Of course, as with any project, numerous people contributed in other ways. I would like to thank the (extended) Page, Symonds, Gould and Hunkin families and my friends Stan and Paul, Gavin and Heather and Fry's Hockey Club for their support, and providing an escape from work; Maisie, you still owe me a "Busy Bee" for helping with your homework. The book could not have been completed without the help and guidance of Wayne Wheeler, Catherine Brett and Simon Rees at Springer-Verlag. It probably would not have been started at all without the encouragement and tutelage of Nigel Smart, Henk Muller, David May and James Irwin within the Computer Science Department at the University of Bristol. Staff and students in the Cryptography and Information Security Group have provided a constant sounding board for ideas; I would like to thank Andrew Moss, Rob Granger, Philipp Grabher and Johann Großschädl in particular. Like all good Engineers, students at the University of Bristol have never been shy to say when I am talking nonsense or present something in a particularly boring way; my thanks to them and many anonymous reviewers for improving the editorial quality throughout.

Most of all I thank Kate for making it all worthwhile.

# **Contents**

# Part I Tools and Techniques

| 1 | Mat  | hemati  | cal Preliminaries                   | 3  |

|---|------|---------|-------------------------------------|----|

|   | 1.1  | Propos  | sitions and Predicates              | 3  |

|   |      | 1.1.1   | Connectives                         | 5  |

|   |      | 1.1.2   | Quantifiers                         | 7  |

|   |      | 1.1.3   | Manipulation                        | 8  |

|   | 1.2  | Sets an | nd Functions                        | 10 |

|   |      | 1.2.1   | Construction                        | 11 |

|   |      | 1.2.2   | Operations                          | 12 |

|   |      | 1.2.3   | Numeric Sets                        | 14 |

|   |      | 1.2.4   | Functions                           | 14 |

|   |      | 1.2.5   | Relations                           | 17 |

|   | 1.3  | Boolea  | an Algebra                          | 18 |

|   |      | 1.3.1   | Boolean Functions                   | 21 |

|   |      | 1.3.2   | Normal Forms                        | 22 |

|   | 1.4  | Numb    | er Systems                          | 23 |

|   |      | 1.4.1   | Converting Between Bases            | 25 |

|   |      | 1.4.2   | Bits, Bytes and Words               | 27 |

|   |      | 1.4.3   | Representing Numbers and Characters | 29 |

|   | 1.5  | Towar   | d a Digital Logic                   | 40 |

|   | 1.6  |         | er Reading                          | 41 |

|   | 1.7  | Examp   | ple Questions                       | 42 |

| 2 | Basi | cs of D | igital Logic                        | 43 |

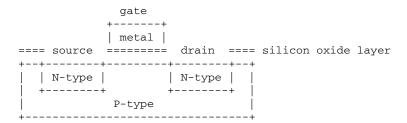

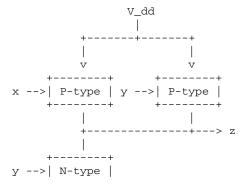

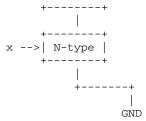

|   | 2.1  | Switch  | nes and Transistors                 | 43 |

|   |      | 2.1.1   | Basic Physics                       | 43 |

|   |      | 2.1.2   | Building and Packaging Transistors  | 44 |

|   | 2.2  | Comb    | inatorial Logic                     | 48 |

|   |      | 2.2.1   | Basic Logic Gates                   | 48 |

|   |      | 2.2.2   | 3-state Logic                       | 50 |

xvi Contents

|   |     | 2.2.3   | Designing Circuits                     | 51 |

|---|-----|---------|----------------------------------------|----|

|   |     | 2.2.4   | Simplifying Circuits                   | 53 |

|   |     | 2.2.5   | Physical Circuit Properties            | 61 |

|   |     | 2.2.6   |                                        | 63 |

|   | 2.3 | Clock   | ed and Stateful Logic                  | 74 |

|   |     | 2.3.1   | Clocks                                 | 75 |

|   |     | 2.3.2   | Latches                                | 77 |

|   |     | 2.3.3   | Flip-Flops                             | 80 |

|   |     | 2.3.4   | State Machines                         | 81 |

|   | 2.4 | Imple   | mentation and Fabrication Technologies | 87 |

|   |     | 2.4.1   | Silicon Fabrication                    | 87 |

|   |     | 2.4.2   | Programmable Logic Arrays              | 90 |

|   |     | 2.4.3   | Field Programmable Gate Arrays         | 92 |

|   | 2.5 | Furthe  | er Reading                             | 93 |

|   | 2.6 |         | ple Questions                          | 93 |

|   |     |         |                                        |    |

| 3 | Har |         | 8 8                                    | 97 |

|   | 3.1 | Introd  |                                        | 97 |

|   |     | 3.1.1   |                                        | 97 |

|   |     | 3.1.2   | Design Automation as a Solution        | 98 |

|   | 3.2 | Struct  | ural Design                            |    |

|   |     | 3.2.1   | Modules                                | 00 |

|   |     | 3.2.2   | Wires                                  | 01 |

|   |     | 3.2.3   | Values and Constants                   | 03 |

|   |     | 3.2.4   | Comments                               | 04 |

|   |     | 3.2.5   | Basic Instantiation 1                  | 05 |

|   |     | 3.2.6   | Nested Instantiation                   | 08 |

|   |     | 3.2.7   | User-Defined Primitives                | 08 |

|   | 3.3 | Highe   | r-level Constructs 1                   | 09 |

|   |     | 3.3.1   | Continuous Assignments                 |    |

|   |     | 3.3.2   | Selection and Concatenation            | 12 |

|   |     | 3.3.3   | Reduction                              | 14 |

|   |     | 3.3.4   | Timing and Delays                      | 14 |

|   | 3.4 | State a | and Clocked Design                     | 15 |

|   |     | 3.4.1   | Registers                              | 15 |

|   |     | 3.4.2   | Processes and Triggers                 | 17 |

|   |     | 3.4.3   | Procedural Assignments                 | 18 |

|   |     | 3.4.4   | Timing and Delays                      | 20 |

|   |     | 3.4.5   | Further Behavioural Statements         | 21 |

|   |     | 3.4.6   | Tasks and Functions                    | 26 |

|   | 3.5 | Effect  | ive Development                        | 27 |

|   |     | 3.5.1   | System Tasks                           | 28 |

|   |     | 3.5.2   | Using the Pre-processor                | 29 |

|   |     | 3.5.3   | Parameters                             |    |

|   |     | 3.5.4   | Named Port Lists                       | 32 |

|     |         | 3.5.5 Generate Statements              |

|-----|---------|----------------------------------------|

|     |         | 3.5.6 Simulation and Stimuli           |

|     | 3.6     | Further Reading                        |

|     | 3.7     | Example Questions                      |

| Pai | rt II I | Processor Design                       |

| 4   | A H     | listorical and Functional Perspective  |

|     | 4.1     | Introduction                           |

|     | 4.2     | Special-Purpose Computers              |

|     | 4.3     | General-Purpose Computers              |

|     | 4.4     | Stored Program Computers               |

|     | 4.5     | Toward Modern Computers                |

|     |         | 4.5.1 The von Neumann Bottleneck       |

|     |         | 4.5.2 Data-Dependent Control-Flow      |

|     |         | 4.5.3 Self-Modifying Programs          |

|     | 4.6     | Further Reading                        |

|     | 4.7     | Example Questions                      |

|     |         |                                        |

| 5   |         | ic Processor Design                    |

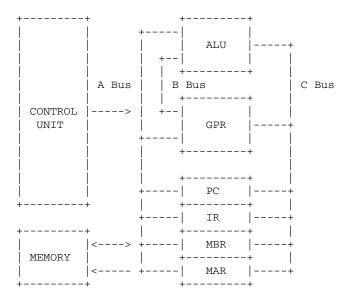

|     | 5.1     | A Concrete Stored Program Architecture |

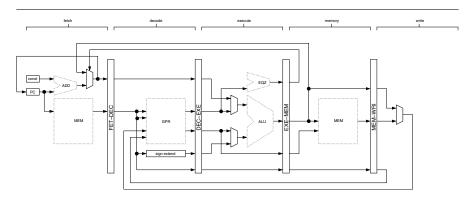

|     |         | 5.1.1 Major Data-path Components       |

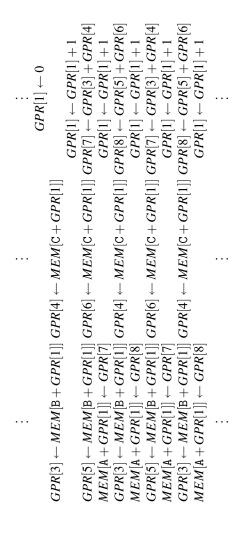

|     |         | 5.1.2 Describing Instruction Behaviour |

|     |         | 5.1.3 The Fetch-Decode-Execute Cycle   |

|     |         | 5.1.4 Controlling the Data-path        |

|     | 5.2     | Buses                                  |

|     |         | 5.2.1 Synchronous Buses                |

|     |         | 5.2.2 Asynchronous Buses               |

|     | 5.3     | Addressing Modes                       |

|     |         | 5.3.1 Immediate Addressing             |

|     |         | 5.3.2 Register Addressing              |

|     |         | 5.3.3 Memory Addressing                |

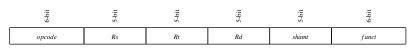

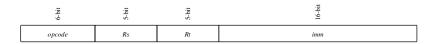

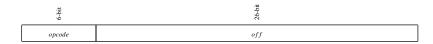

|     | 5.4     | Instruction Encoding                   |

|     |         | 5.4.1 Instruction Selection            |

|     |         | 5.4.2 Instruction Formats              |

|     |         | 5.4.3 Basic Encoding and Decoding      |

|     |         | 5.4.4 More Complicated Encoding Issues |

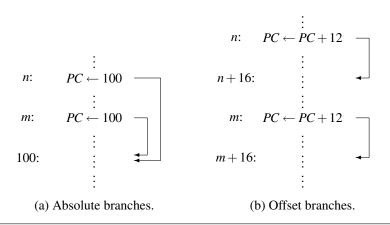

|     | 5.5     | Control-Flow                           |

|     |         | 5.5.1 Predicated Execution             |

|     | ~ ~     | 5.5.2 Function Calls                   |

|     | 5.6     | Some Design Philosophy                 |

|     |         | 5.6.1 Moore's Law                      |

|     |         | 5.6.2 RISC versus CISC                 |

|     | 5.7     | Putting It All Together                |

|     | 5.8     | Further Reading                        |

|     | 5.9     | Example Questions                      |

xviii Contents

| 6 | Mos  | curina  | Performance                              | 212 |

|---|------|---------|------------------------------------------|-----|

| U | 6.1  |         | ring Performance                         |     |

|   | 0.1  | 6.1.1   |                                          |     |

|   |      | 6.1.2   | Estimating Execution Time                |     |

|   |      |         | Measuring Execution Time                 |     |

|   |      | 6.1.3   | Benchmark Programs                       |     |

|   |      | 6.1.4   | Measuring Improvement                    |     |

|   | 6.2  |         | r Reading                                |     |

|   | 6.3  | Examp   | ole Questions                            | 220 |

| 7 | Arit | hmetic  | and Logic                                | 223 |

|   | 7.1  | Introdu | action                                   | 223 |

|   | 7.2  |         | arisons                                  |     |

|   |      | 7.2.1   | Unsigned Comparisons                     |     |

|   |      | 7.2.2   | Signed Comparisons                       |     |

|   | 7.3  | Additio | on and Subtraction                       |     |

|   |      | 7.3.1   | Addition                                 |     |

|   |      | 7.3.2   | Subtraction                              |     |

|   | 7.4  |         | nd Rotate                                |     |

|   |      | 7.4.1   | Bit-Serial Shifter                       |     |

|   |      | 7.4.2   | Logarithmic Shifter                      |     |

|   | 7.5  |         | lication                                 |     |

|   |      | 7.5.1   | Bit-Serial Multiplier                    |     |

|   |      | 7.5.2   | Tree Multiplier                          |     |

|   |      | 7.5.3   | Digit-Serial Multiplier                  |     |

|   |      | 7.5.4   | Early Termination                        |     |

|   |      | 7.5.5   | Wallace and Dadda Trees                  |     |

|   |      | 7.5.6   | Booth Recoding                           |     |

|   | 7.6  |         | g It All Together                        |     |

|   | ,,,  | 7.6.1   | Comparison ALU                           |     |

|   |      | 7.6.2   | Arithmetic ALU                           |     |

|   | 7.7  |         | r Reading                                |     |

|   | 7.8  |         | ole Questions                            |     |

|   | 7.0  | Daning  | ie destrois                              | 200 |

| 8 | Mer  |         | d Storage                                |     |

|   | 8.1  | Introdu | action                                   |     |

|   |      | 8.1.1   | Historical Memory and Storage            |     |

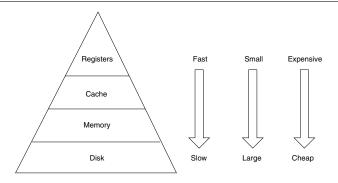

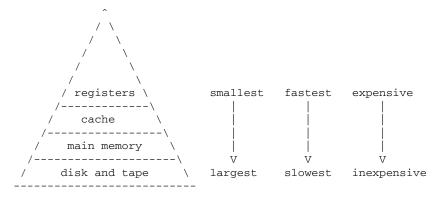

|   |      | 8.1.2   | A Modern Memory Hierarchy                |     |

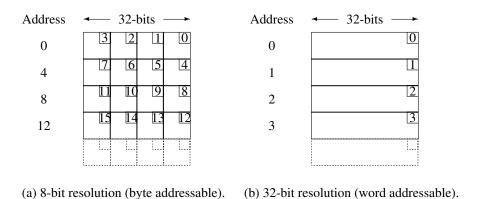

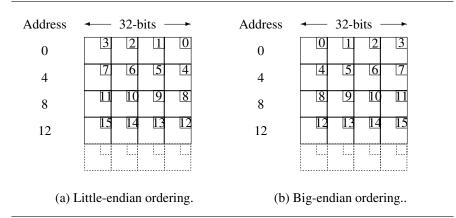

|   |      | 8.1.3   | Basic Organisation and Implementation    |     |

|   |      | 8.1.4   | Memory Banking                           |     |

|   |      | 8.1.5   | Access Locality                          |     |

|   | 8.2  | Memo    | ry and Storage Specifics                 |     |

|   |      | 8.2.1   | Static RAM (SRAM) and Dynamic RAM (DRAM) | 291 |

|   |      | 8.2.2   | Non-volatile RAM and ROM                 | 293 |

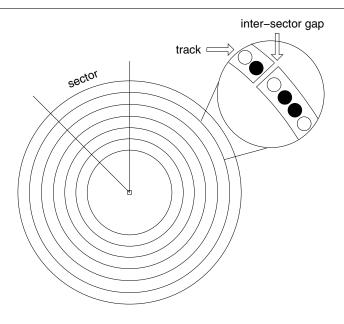

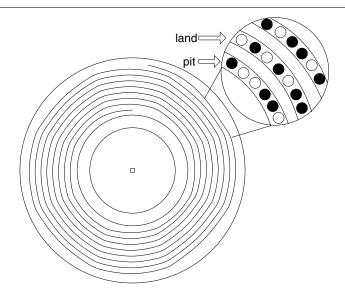

|   |      | 8.2.3   | Magnetic Disks                           | 294 |

Contents xix

|   |     | 8.2.4   | Optical Disks                            |       |

|---|-----|---------|------------------------------------------|-------|

|   | 0.2 | 8.2.5   | Error Correction                         |       |

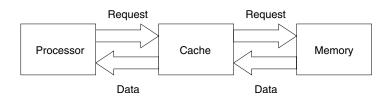

|   | 8.3 |         | Cache Memories                           |       |

|   |     | 8.3.1   | Fetch Policy                             |       |

|   |     | 8.3.2   | Write Policy                             |       |

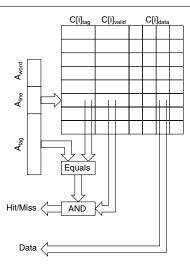

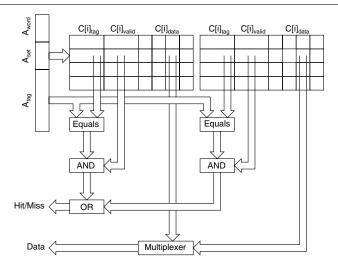

|   |     | 8.3.3   | Direct-Mapped Caches                     |       |

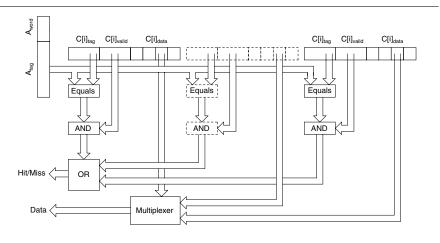

|   |     | 8.3.4   | Fully-Associative Caches                 |       |

|   |     | 8.3.5   | Set-Associative Caches                   |       |

|   | 0.4 | 8.3.6   | Cache Organisation                       |       |

|   | 8.4 |         | nced Cache Memories                      |       |

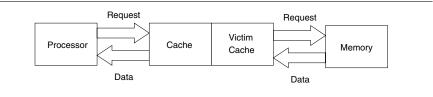

|   |     | 8.4.1   | Victim Caches                            |       |

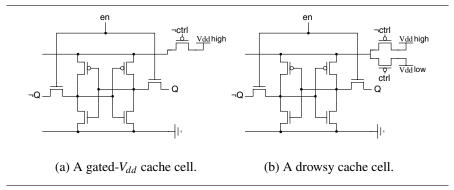

|   | 0.5 | 8.4.2   | Gated and Drowsy Caches                  |       |

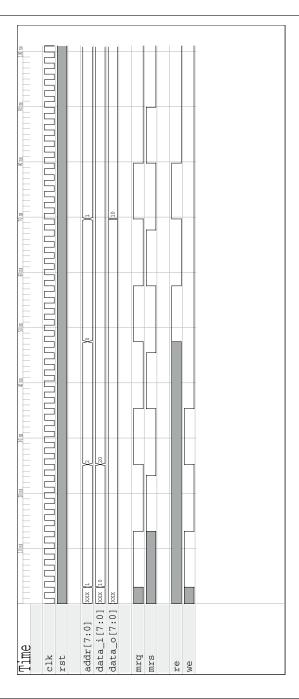

|   | 8.5 |         | g It All Together                        |       |

|   |     | 8.5.1   | Register File                            |       |

|   |     | 8.5.2   | Main Memory                              |       |

|   |     | 8.5.3   | Cache Memory                             |       |

|   | 8.6 |         | er Reading                               |       |

|   | 8.7 | Exam    | ple Questions                            | . 329 |

| 9 | Adv |         | Processor Design                         |       |

|   | 9.1 | Introd  | uction                                   |       |

|   |     | 9.1.1   | A Taxonomy of Parallelism                |       |

|   |     | 9.1.2   | Instruction-Level Parallelism (ILP)      |       |

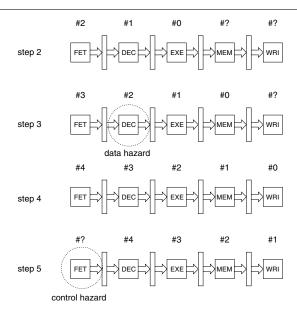

|   | 9.2 | Pipelii | ned Processors                           |       |

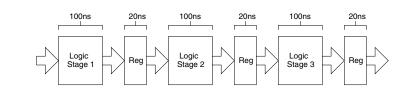

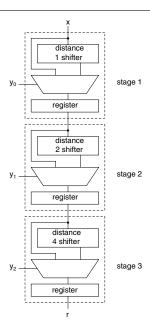

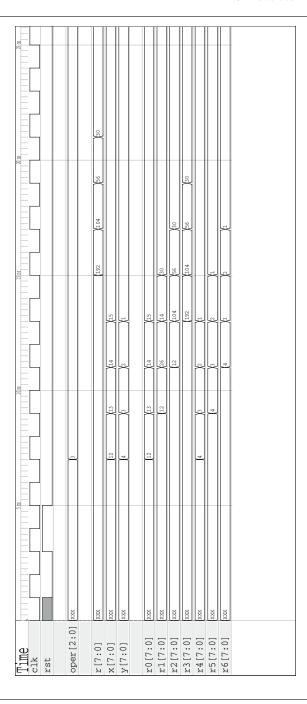

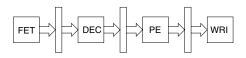

|   |     | 9.2.1   | Pipelined Circuits                       |       |

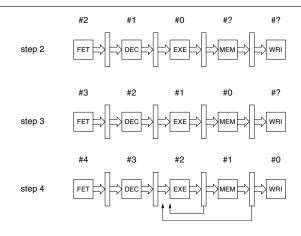

|   |     | 9.2.2   | Pipelined Processors                     |       |

|   |     | 9.2.3   | Pipeline Hazards                         |       |

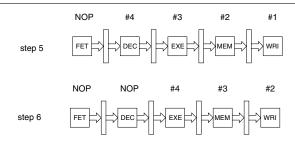

|   |     | 9.2.4   | Stalls and Hazard Resolution             |       |

|   | 9.3 | Supers  | scalar Processors                        | . 360 |

|   |     | 9.3.1   | Basic Concept                            | . 360 |

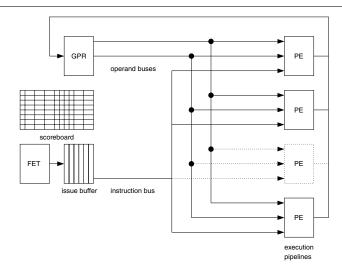

|   |     | 9.3.2   | Step 1: Scoreboard-based Design          | . 361 |

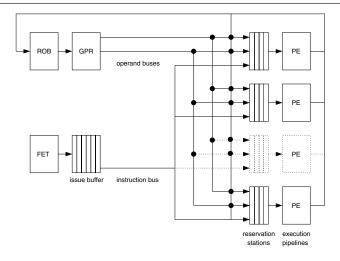

|   |     | 9.3.3   | Step 2: Reservation Station-based Design | . 370 |

|   |     | 9.3.4   | Further Improvements                     | . 378 |

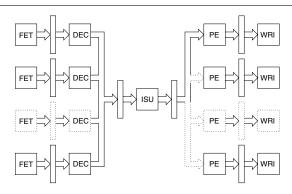

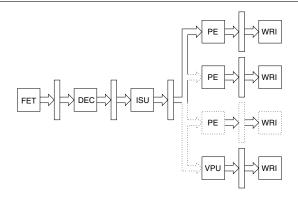

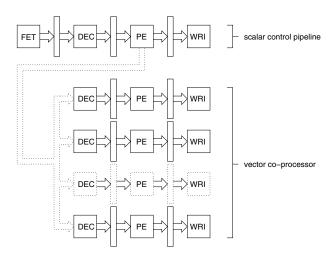

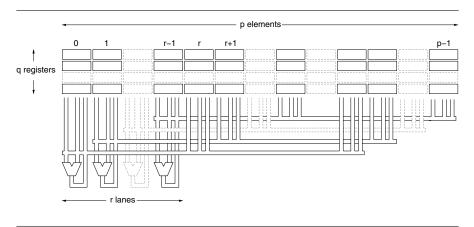

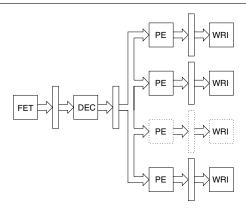

|   | 9.4 | Vector  | r Processors                             | . 380 |

|   |     | 9.4.1   | Basic Concept                            | . 380 |

|   |     | 9.4.2   | A Dedicated Vector Processor             | . 382 |

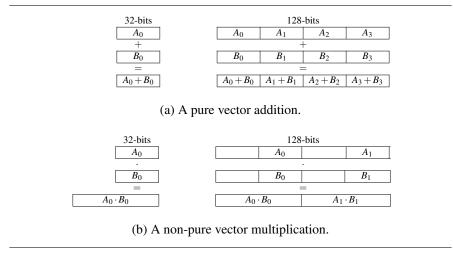

|   |     | 9.4.3   | SIMD Within A Register (SWAR)            | . 384 |

|   |     | 9.4.4   | Issues of Vectorisation                  |       |

|   | 9.5 | VLIW    | Processors                               |       |

|   |     | 9.5.1   | Basic Concept                            |       |

|   | 9.6 | Furthe  | er Reading                               |       |

|   | 9.7 |         | ple Questions                            |       |

|   |     |         |                                          |       |

xx Contents

# Part III The Hardware/Software Interface

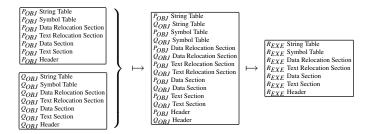

| 10 | Linkers and Assemblers                                        | 397 |

|----|---------------------------------------------------------------|-----|

|    | 10.1 Introduction                                             | 397 |

|    | 10.2 The Memory Model                                         | 400 |

|    | 10.2.1 Stack Section                                          | 401 |

|    | 10.2.2 Static Data Section                                    | 402 |

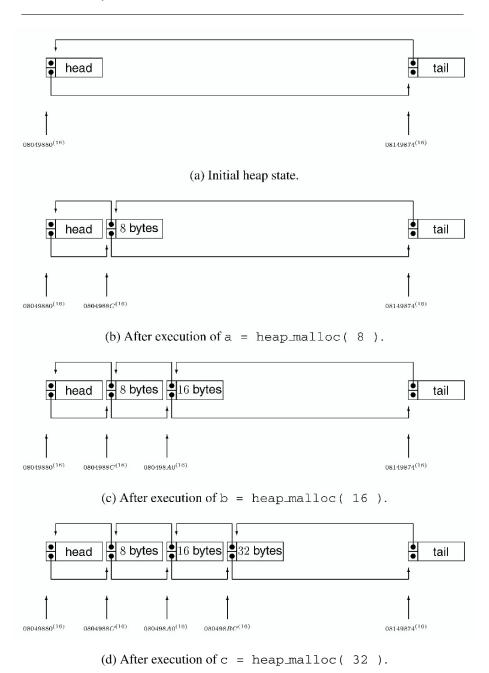

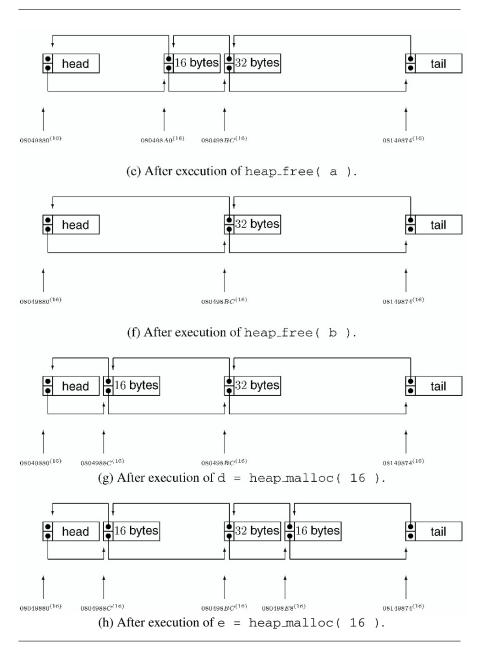

|    | 10.2.3 Dynamic Data Section                                   |     |

|    | 10.3 Executable Versus Object Files                           |     |

|    | 10.4 Linkers                                                  |     |

|    | 10.4.1 Static and Dynamic Linkage                             |     |

|    | 10.4.2 Boot-strap Functions                                   |     |

|    | 10.4.3 Symbol Relocation                                      |     |

|    | 10.4.4 Symbol Resolution                                      |     |

|    | 10.5 Assemblers                                               |     |

|    | 10.5.1 Basic Assembly Language Statements                     |     |

|    | 10.5.2 Using Machine Instructions                             |     |

|    | 10.5.3 Using Assembler Aliases                                |     |

|    | 10.5.4 Using Assembler Directives                             |     |

|    | 10.5.5 Peephole Optimisation                                  |     |

|    | 10.5.6 Some Short Example Programs                            |     |

|    | 10.5.7 The Forward Referencing Problem                        |     |

|    | 10.5.8 An Example Assembler                                   |     |

|    | 10.6 Further Reading                                          |     |

|    | 10.7 Example Questions                                        |     |

|    | 10.7 Example Questions                                        |     |

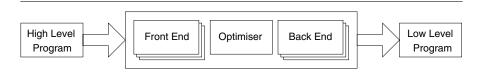

| 11 | Compilers                                                     | 451 |

|    | 11.1 Introduction                                             | 451 |

|    | 11.2 Compiler Bootstrapping and Re-Hosting                    | 453 |

|    | 11.3 Intermediate Representation                              | 454 |

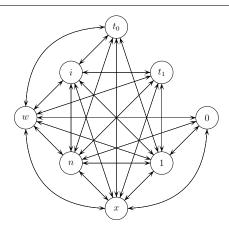

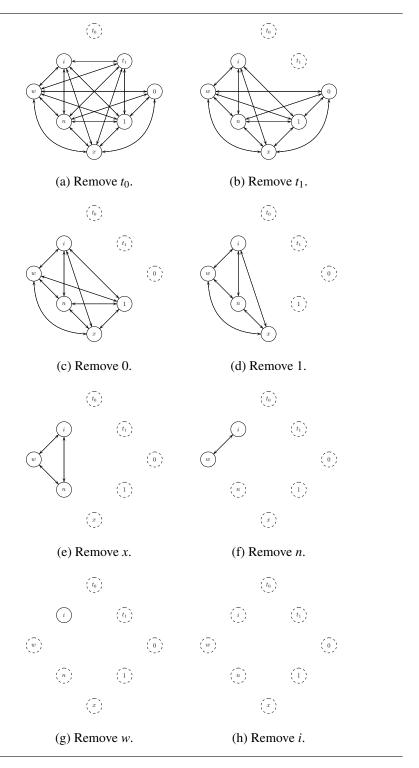

|    | 11.4 Register Allocation                                      |     |

|    | 11.4.1 An Example Allocation                                  |     |

|    | 11.4.2 Uses for Pre-colouring                                 | 463 |

|    | 11.4.3 Avoiding Error Cases via Spilling                      |     |

|    | 11.5 Instruction Selection and Scheduling                     |     |

|    | 11.5.1 Instruction Selection                                  |     |

|    | 11.5.2 Instruction Scheduling                                 |     |

|    | 11.5.3 Scheduling Basic Blocks                                |     |

|    | 11.5.4 Scheduling Instructions                                |     |

|    | 11.6 "Template" Code Generation for High-Level Statements     |     |

|    | 11.6.1 Conditional Statements                                 |     |

|    | 11.6.2 Loop Statements                                        |     |

|    | 11.6.3 Multi-way Branch Statements                            |     |

|    | 11.7 "Template" Code Generation for High-Level Function Calls |     |

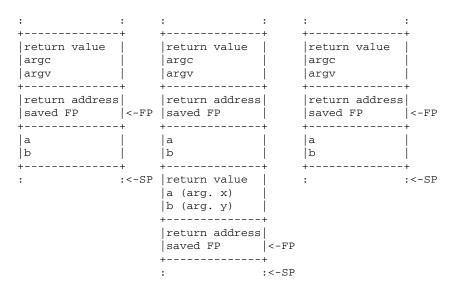

|    | 11.7.1 Basic Stack Frames                                     |     |

|    |                                                               |     |

Contents xxi

|    |       | 11.7.2 Advanced Stack Frames                 | . 485 |

|----|-------|----------------------------------------------|-------|

|    | 11.8  | Further Reading                              | . 491 |

|    | 11.9  | Example Questions                            | . 492 |

|    |       |                                              |       |

| 12 |       | rating Systems                               |       |

|    |       | Introduction                                 |       |

|    | 12.2  | The Hardware/Software Interface              | . 497 |

|    |       | 12.2.1 MIPS32 Co-processor Registers         | . 497 |

|    |       | 12.2.2 MIPS32 Processor Modes                | . 499 |

|    |       | 12.2.3 MIPS32 Assembly Language              | . 500 |

|    | 12.3  | Boot-Strapping                               | . 501 |

|    | 12.4  | Event Management                             | . 502 |

|    |       | 12.4.1 Handling Interrupts                   | . 503 |

|    |       | 12.4.2 Handling Exceptions                   | . 505 |

|    |       | 12.4.3 Handling Traps                        | . 506 |

|    |       | 12.4.4 An Example Exception Handler          |       |

|    | 12.5  | Memory Management                            |       |

|    |       | 12.5.1 Basic Concept                         |       |

|    |       | 12.5.2 Pages and Frames                      |       |

|    |       | 12.5.3 Address Translation and Memory Access |       |

|    |       | 12.5.4 Page Eviction and Replacement         |       |

|    |       | 12.5.5 Translation Look-aside Buffer (TLB)   |       |

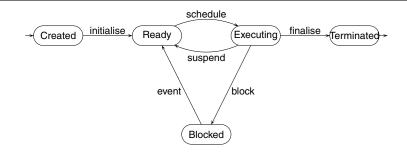

|    | 12.6  | Process Management                           |       |

|    |       | 12.6.1 Storing and Switching Process Context |       |

|    |       | 12.6.2 Process Scheduling                    |       |

|    |       | 12.6.3 An Example Scheduler                  |       |

|    | 12.7  | Further Reading                              |       |

|    |       | Example Questions                            |       |

|    |       |                                              |       |

| 13 | Effic | cient Programming                            | . 535 |

|    | 13.1  | Introduction                                 | . 535 |

|    | 13.2  | "Space" Conscious Programming                | . 536 |

|    |       | 13.2.1 Reducing Register Pressure            | . 536 |

|    |       | 13.2.2 Reducing Memory Allocation            | . 537 |

|    | 13.3  | "Time" Conscious Programming                 |       |

|    |       | 13.3.1 Effective Short-circuiting            | . 540 |

|    |       | 13.3.2 Branch Elimination                    |       |

|    |       | 13.3.3 Loop Fusion and Fission               | . 542 |

|    |       | 13.3.4 Loop Unrolling                        |       |

|    |       | 13.3.5 Loop Hoisting                         |       |

|    |       | 13.3.6 Loop Interchange                      |       |

|    |       | 13.3.7 Loop Blocking                         |       |

|    |       | 13.3.8 Function Inlining                     |       |

|    |       | 13.3.9 Software Pipelining                   |       |

|    | 13.4  | Example Questions                            |       |

|    |       |                                              |       |

xxii Contents

| SPIM: A  | MIPS32 Simulator          | 561 |

|----------|---------------------------|-----|

| A.1      | Introduction              | 561 |

| A.2      | Configuring SPIM          | 562 |

| A.3      | Controlling SPIM          | 563 |

|          | Example Program Execution |     |

| A.5      | Using System Calls        | 570 |

| Example  | Solutions                 | 573 |

| Referenc | es                        | 629 |

| Index    |                           | 633 |

# Part I Tools and Techniques

# Chapter 1 Mathematical Preliminaries

In mathematics you don't understand things. You just get used to them.

- J. von Neumann

Abstract The goal of this chapter is to give a fairly comprehensive overview of the theory that underpins the rest of the book. On first reading, it may seem a little dry and is often excluded in other similar books. However, without a solid understanding of logic and representation of numbers it seems clear that constructing digital circuits to put this theory into practise would be much harder. The theory here will present an introduction to propositional logic, sets and functions, number systems and Boolean algebra. These four main areas combine to produce a basis for formal methods to describe, manipulate and implement digital systems such as computer processors. Those with a background in mathematics or computer science might skip this material and use it simply for reference; those approaching the subject from another background would be advised to read the material in more detail.

# 1.1 Propositions and Predicates

**Definition 1.** A **proposition** is a statement whose meaning, termed the **truth value**, is either true or false. Less formally, we say the statement is true if it has a truth value of true and false if it has a truth value of false.

A **predicate** is a proposition which contains one or more **variables**; only when concrete values are **assigned** to each of the variables can the predicate be called a proposition.

Since we use them so naturally, it almost seems too formal to define what a proposition is. However, by doing so we can start to use them as a building block to describe what logic is and how it works. The statement

"the temperature is  $90^{\circ}C$ "

is a proposition since it is definitely either true or false. When we take a proposition and decide whether it is true or false, we say we have **evaluated** it. However, there are clearly a lot of statements that are not propositions because they do not state any proposal. For example,

"turn off the heat"

is a command or request of some kind, it does not evaluate to a truth value. Propositions must also be well defined in the sense that they are definitely either true or false, i.e., there are no "gray areas" in between. The statement

" $90^{\circ}C$  is too hot"

is not a proposition since it could be true or false depending on the context, or your point of view:  $90^{\circ}C$  probably is too hot for body temperature but probably not for a cup of coffee. Finally, some statements look like propositions but cannot be evaluated because they are paradoxical. The most famous example of this situation is the liar paradox, usually attributed to the Greek philosopher Eubulides, who stated it as

"a man says that he is lying, is what he says true or false?"

although a clearer version is the more commonly referenced

"this statement is false".

If the man is telling the truth, everything he says must be true which means he is lying and hence everything he says is false. Conversely, if the man is lying everything he says is false, so he cannot be lying since he said he was! In terms of the statement, we cannot be sure of the truth value so this is not normally classed as a proposition.

As stated above, a predicate is just a proposition that contains variables. By **assigning** the variable a value we can turn the predicate into a proposition and evaluate the corresponding truth value. For example, consider the predicate

"

$$x^{\circ}C$$

equals  $90^{\circ}C$ "

where x is a variable. By assigning x a value we get a proposition; setting x = 10, for example, gives

" $10^{\circ}C$  equals  $90^{\circ}C$ "

which clearly evaluates to false. Setting  $x = 90^{\circ}C$  gives

"90° C equals  $90^{\circ}$  C"

which evaluates to true. In some sense, a predicate is an abstract or general proposition which is not well defined until we assign values to all the variables.

### 1.1.1 Connectives

**Definition 2.** A **connective** is a statement which binds single propositions into a compound proposition. For brevity, we use symbols to denote common connectives:

- "not x" is denoted  $\neg x$ .

- "x and y" is denoted  $x \wedge y$ .

- "x or y" is denoted  $x \lor y$ , this is usually called an inclusive-or.

- "x or y but not x and y" is denoted  $x \oplus y$ , this is usually called an exclusive-or.

- "x implies y" is denoted  $x \rightarrow y$ , which is sometimes written as "if x then y".

- "x is equivalent to y" is denoted  $x \leftrightarrow y$ , which is sometimes written as "x if and only if y" or further shortened to "x iff. y".

Note that we group statements using parentheses when there could be some confusion about the order they are applied; hence  $(x \land y)$  is the same as  $x \land y$ .

A proposition or predicate involving connectives is built from **terms**; the connective joins together these terms into an **expression**. For example, the expression

"the temperature is less than  $90^{\circ}C$   $\wedge$  the temperature is greater than  $10^{\circ}C$ " contains two terms that propose

"the temperature is less than  $90^{\circ}C$ "

and

"the temperature is greater than  $10^{\circ}C$ ".

These terms are joined together using the  $\land$  connective so that the whole expression evaluates to true if both of the terms are true, otherwise it evaluates to false. In a similar way we might write a compound predicate

"the temperature is less than  $x^{\circ}C \wedge$  the temperature is greater than  $y^{\circ}C$ "

which can only be evaluated when we assign values to the variables x and y.

**Definition 3.** The meaning of connectives is usually describe in a tabular form which enumerates the possible values each term can take and what the resulting truth value is; we call this a **truth table**.

| X     | у     | $\neg x$ | $x \wedge y$ | $x \vee y$ | $x \oplus y$ | $x \rightarrow y$ | $x \leftrightarrow y$ |

|-------|-------|----------|--------------|------------|--------------|-------------------|-----------------------|

| false | false | true     | false        | false      | false        | true              | true                  |

| false | true  | true     | false        | true       | true         | true              | false                 |

| true  | false | false    | false        | true       | true         | false             | false                 |

| true  | true  | false    | true         | true       | false        | true              | true                  |

The  $\neg$  connective negates the truth value of an expression so considering

$$\neg (x > 10)$$

we find that the expression  $\neg(x > 10)$  is true if the term x > 10 is false and the expression is false if x > 10 is true. If we assign x = 9, x > 10 is false and hence the expression  $\neg(x > 10)$  is true. If we assign x = 91, x > 10 is true and hence the expression  $\neg(x > 10)$  is false.

The meaning of the ∧ connective is also as one would expect; the expression

$$(x > 10) \land (x < 90)$$

is true if *both* the expressions x > 10 and x < 90 are true, otherwise it is false. So if x = 20, the expression is true. But if x = 9 or x = 91, then it is false: even though one or other of the terms is true, they are not both true.

The inclusive-or and exclusive-or connectives are fairly similar. The expression

$$(x > 10) \lor (x < 90)$$

is true if *either* x > 10 *or* x < 90 is true or both of them are true. Here we find that all the assignments x = 20, x = 9 and x = 91 mean the expression is true; in fact it is hard to find an x for which it evaluates to false! Conversely, the expression

$$(x > 10) \oplus (x < 90)$$

is only true if *only one* of either x > 10 or x < 90 is true; if they are both true then the expression is false. We now find that setting x = 20 means the expression is false while both x = 9 and x = 91 mean it is true.

Inference is a bit more tricky. If we write  $x \rightarrow y$ , we usually call x the **hypothesis** and y the **conclusion**. To justify the truth table for inference in words, consider the example

$$(x \text{ is prime }) \land (x \neq 2) \rightarrow (x \equiv 1 \pmod{2})$$

i.e., if x is a prime other than 2, it follows that it is odd. Therefore, if x is prime then the expression is true if  $x \equiv 1 \pmod{2}$  and false otherwise since the implication is invalid. If x is not prime, the expression does not really say anything about the expected outcome: we only know what to expect if x was prime. Since it could still be that  $x \equiv 1 \pmod{2}$  even when x is not prime, and we do not know anything better from the expression, we assume it is true when this case occurs.

Equivalence is fairly simple. The expression  $x \leftrightarrow y$  is only true if x and y evaluate to the same value. This matches the idea of equality of numbers. As an example, consider

$$(x \text{ is odd}) \leftrightarrow (x \equiv 1 \pmod{2}).$$

This expression is true since if the left side is true, the right side must also be true and vice versa. If we change it to

$$(x \text{ is odd}) \leftrightarrow (x \text{ is prime}),$$

then the expression is false. To see this, note that only some odd numbers are prime: just because a number is odd does not mean it is always prime although if it is prime

it must be odd (apart from the corner case of x = 2). So the equivalence works in one direction but not the other and hence the expression is false.

**Definition 4.** We call two expressions logically **equivalent** if they are composed of the same variables and have the same truth value for every possible assignment to those variables.

An expression which is equivalent to true, no matter what values are assigned to any variables, is called a **tautology**; an expression which is equivalent to false is called a **contradiction**.

Some subtleties emerge when trying to prove two expressions are logically equivalent. However, we will skirt around these. For our purposes it suffices to simply enumerate all possible values each variable can take, and check the two expressions produce identical truth values in all cases. In practise this can be hard since with n variables there will be  $2^n$  possible assignments, an amount which grows quickly as n grows! More formally, two expressions x and y are only equivalent if  $x \leftrightarrow y$  can be proved a tautology.

### 1.1.2 Quantifiers

**Definition 5.** A **free variable** in a given expression is one which has not yet been assigned a value. Roughly speaking, a **quantifier** is a statement which allows a free variable to take one of many values:

- the **universal quantifier** "for all x, y is true" is denoted  $\forall x [y]$ .

- the **existential quantifier** "there exists an x such that y is true" is denoted  $\exists x [y]$ .

We say that applying a quantifier to a variable quantifies it; after it has been quantified we say it has been **bound**.

Put more simply, when we encounter an expression such as

$$\exists x [y]$$

we are essentially assigning x all possible values; to make the expression true *just one* of these values needs to make the expression y true. Likewise, when we encounter

$$\forall x [y]$$

we are again assigning *x* all possible values. This time however, to make the expression true, *all of them* need to make the expression *y* true. Consider the following example:

"there exists an x such that  $x \equiv 0 \pmod{2}$ "

which we can re-write symbolically as

$$\exists x [x \equiv 0 \pmod{2}].$$

In this case, x is bound by the  $\exists$  quantifier; we are asserting that for some value of x it is true that  $x \equiv 0 \pmod{2}$ . To make the expression true just one of these values needs to make the term  $x \equiv 0 \pmod{2}$  true. The assignment x = 2 satisfies this so the expression is true. As another example, consider the expression

"for all

$$x, x \equiv 0 \pmod{2}$$

"

which we re-write

$$\forall x [x \equiv 0 \pmod{2}].$$

Here we are making a more general assertion about x by saying that for all x, it is true that  $x \equiv 0 \pmod{2}$ . To decide if this particular expression is false, we need simply to find an x such that  $x \not\equiv 0 \pmod{2}$ . This is easy since any odd value of x is good enough. Therefore the expression is false.

**Definition 6.** Informally, a **predicate function** is just a shorthand way of writing predicates; we give the function a name and a list of free variables. So for example the function

$$f(x, y) : x = y$$

is called f and has two variables named x and y. If we use the function as f(10,20), performing the binding x = 10 and y = 20, it has the same meaning as 10 = 20.

# 1.1.3 Manipulation

**Definition 7.** Manipulation of expressions is governed by a number of axiomatic laws:

```

\equiv (x \rightarrow y) \land (y \rightarrow x)

equivalence

x \leftrightarrow y

implication

x \rightarrow y

\equiv \neg x \lor y

involution

\equiv x

\neg \neg x

idempotency

x \wedge x

\equiv x

commutativity x \wedge y

\equiv y \wedge x

association

(x \wedge y) \wedge z \equiv x \wedge (y \wedge z)

x \wedge (y \vee z) \equiv (x \wedge y) \vee (x \wedge z)

distribution

\neg(x \land y) \equiv \neg x \lor \neg y

de Morgan's

identity

x \wedge \text{true}

\equiv x

null

x \wedge \text{false} \equiv \text{false}

inverse

x \land \neg x

\equiv false

absorption

x \land (x \lor y) \equiv x

x \vee x

idempotency

\equiv x

commutativity x \lor y

\equiv y \lor x

association

(x \lor y) \lor z \equiv x \lor (y \lor z)

distribution

x \lor (y \land z) \equiv (x \lor y) \land (x \lor z)

de Morgan's

\neg(x \lor y) \equiv \neg x \land \neg y

x \vee \text{false} \equiv x

identity

x \vee \text{true}

null

\equiv true

x \vee \neg x

inverse

≡ true

absorption

x \lor (x \land y) \equiv x

```

A common reason to manipulate a logic expression is to simplify it in some way so that it contains less terms or less connectives. A simplified expression might be more opaque, in the sense that it is not as clear what it means, but looking at things computationally it will generally be "cheaper" to evaluate. As a concrete example of simplification in action, consider the exclusive-or connective  $x \oplus y$  which we can write as the more complicated expression

$$(y \land \neg x) \lor (x \land \neg y)$$

or even as

$$(x \lor y) \land \neg (x \land y).$$

The first alternative above uses five connectives while the second uses only four; we say that the second is simpler as a result. One can prove that these are equivalent by constructing truth tables for them. The question is, how did we get from one to the other by manipulating the expressions?

To answer this, we simply start with one expression and apply our axiomatic laws to move toward the other. So starting with the first alternative, we try to apply the axioms until we get the second: think of the axioms like rules that allow one to rewrite the expression in a different way. To start with, we can manipulate each term which looks like  $p \land \neg q$  as follows

$$(p \land \neg q) = (p \land \neg q) \lor \text{false} \qquad \text{(identity)}$$

=  $(p \land \neg q) \lor (p \land \neg p) \text{ (null + inverse)}$

=  $p \land (\neg p \lor \neg q) \qquad \text{(distribution)}$

Using this new identity, we can re-write the whole expression as

which gives us the second alternative we are looking for. A later chapter shows how to construct an algorithm to do this sort of simplification mechanically so as to reduce our workload and reduce the chance of error.

### 1.2 Sets and Functions

The concept of a **set** and the theory behind such objects is a fundamental part of mathematics. Informally, a set is simply a well defined collection of **elements**. Here we mainly deal with sets of numbers, but it is important to note that the elements can be anything you want.

We can define a set using one of several methods. Firstly we can enumerate the elements, writing them down between a pair of braces. For example, one might define the set *A* of whole numbers between two and eight (inclusive) as

$$A = \{2, 3, 4, 5, 6, 7, 8\}.$$

The **cardinality** of a finite set is the number of elements it contains. For the set A, this is denoted by |A| such that from the example above

$$|A| = 7.$$

If the element a is in the set A, we say a is a **member** of A or write

$$a \in A$$

.

The ordering of the elements in the set does not matter, only their membership or non-membership. So we can define another set as

$$B = \{8, 7, 6, 5, 4, 3, 2\}$$

and be safe in the knowledge that A = B. However, note that elements cannot occur in a set more than once; a set where repetitions are allowed is sometimes called a **bag** or **multi-set** but is beyond the scope of this discussion.

There are at least two predefined sets which have a clear meaning but are hard to define using any other notation:

**Definition 8.** The set  $\emptyset$ , called the **null set** or **empty set**, is the set which contains no elements. Note that  $\emptyset$  is a set not an element, one cannot write the empty set as  $\{\emptyset\}$  since this is the set with one element, that element being the empty set.

1.2 Sets and Functions

**Definition 9.** The contents of the set  $\mathcal{U}$ , called the **universal set**, depends on the context. Roughly speaking, it contains every element from the problem being considered.

As a side note, since the elements in a set can be anything we want they can potentially be other sets. Russell's paradox, discovered by mathematician Bertrand Russell in 1901, is a problem with formal set theory that results from this fact. The paradox is similar to the liar paradox seen earlier and is easily stated by considering *A*, the set of all sets which do not contain themselves. The question is, does *A* contain itself? If it does, it should not be in *A* by definition but it is; if it does not, it should be in the set *A* by definition but it is not.

### 1.2.1 Construction

The above method of definition is fine for small finite sets but when the set is large or even infinite in size, writing down all the elements quickly becomes an unpleasant task! Where there is a natural sequence to the elements, we write continuation dots to save time and space. For example, the same set *A* as above might be defined as

$$A = \{2, 3, \dots, 7, 8\}.$$

This set is finite since there is a beginning and an end; the continuation dots are simply a shortcut. As another example, consider the set of numbers exactly divisible by two that might be defined as

$$C = \{2, 4, 6, 8, \ldots\}.$$

Clearly this set is infinite in size in the sense there is no end to the sequence. In this case the continuation dots are a necessity in order to define the set adequately.

The second way to write down sets is using what is sometimes called set builder notation. Basically speaking, we generate the elements in the set using f, a predicate function:

$$D = \{x : f(x)\}.$$

One should read this as "all elements  $x \in \mathcal{U}$  such that the predicate f(x) is true". Using set builder notation we can define sets in a more programmatic manner, for example

$$A = \{x : 2 \le x \le 8\},\$$

and

$$C = \{x : x > 0 \land x \equiv 0 \pmod{2}\}$$

define the same sets as we explicitly wrote down above.

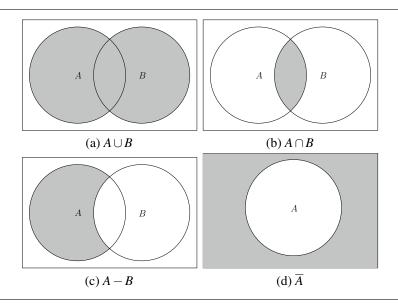

Figure 1.1 A collection of Venn diagrams for standard set operations.

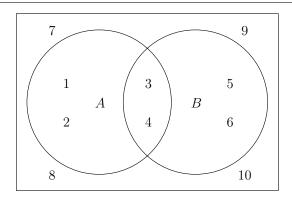

Figure 1.2 An example Venn diagram showing membership of two sets.

# 1.2.2 Operations

**Definition 10.** A **sub-set**, say *B*, of a set *A* is such that for every  $x \in B$  we have that  $x \in A$ . This is denoted  $B \subseteq A$ . Conversely, we can say *A* is a **super-set** of *B* and write  $A \supseteq B$ .

1.2 Sets and Functions 13

Note that every set is a sub-set and super-set of itself and that A = B only if  $A \subseteq B$  and  $B \subseteq A$ . If  $A \neq B$ , we use the terms **proper sub-set** and **proper super-set** and write  $B \subset A$  and  $B \supset A$  respectively.

### **Definition 11.** For sets A and B, we have that

- The **union** of *A* and *B* is  $A \cup B = \{x : x \in A \lor x \in B\}$ .

- The **intersection** of *A* and *B* is  $A \cap B = \{x : x \in A \land x \in B\}$ .

- The **difference** of *A* and *B* is  $A B = \{x : x \in A \land x \notin B\}$ .

- The **complement** of *A* is  $\overline{A} = \{x : x \in \mathcal{U} \land x \notin A\}$ .

We say *A* and *B* are **disjoint** or **mutually exclusive** if  $A \cap B = \emptyset$ . Note also that the complement operation can be re-written  $A - B = A \cap \overline{B}$ .

**Definition 12.** The power set of a set A, denoted  $\mathcal{P}(A)$ , is the set of every possible sub-set of A. Note that  $\emptyset$  is a member of all power sets.

On first reading, these formal definitions can seem a bit abstract and slightly scary. However, we have another tool at our disposal which describes what they mean in a visual way. This tool is the **Venn diagram**, named after mathematician John Venn who invented the concept in 1881. The basic idea is that sets are represented by regions inside an enclosure that implicitly represents the universal set  $\mathscr{U}$ . By placing these regions inside each other and overlapping their boundaries, we can describe most set-related concepts very easily.

Figure 1.1 details four Venn diagrams which describe how the union, intersection, difference and complement operations work. The shaded areas of each Venn diagram represent the elements which are in the resulting set. For example, in the diagram for  $A \cup B$  the shaded area covers all of the sets A and B: the result contains all elements in either A or B or both. As a simple concrete example, consider the sets

$$A = \{1,2,3,4\}$$

$B = \{3,4,5,6\}$

where the universal set is

$$\mathcal{U} = \{1, 2, 3, 4, 5, 6, 7, 8, 9, 10\}.$$

Figure 1.2 shows membership in various settings; recall that those elements within a given region are members of that set. Firstly, we can take the union of A and B as  $A \cup B = \{1,2,3,4,5,6\}$  which contains all the elements which are either members of A or B or both. Note that elements 3 and 4 do not appear twice in the result. The intersection of A and B can be calculated as  $A \cap B = \{3,4\}$  since these are the elements that are members of both A and B. The difference between A and B, that is the elements in A that are not in B, is  $A - B = \{1,2\}$ . Finally, the complement of A is all numbers which are not in A, that is  $\overline{A} = \{5,6,7,8,9,10\}$ .

The union and intersection operations preserve a law of cardinality called the **principle of inclusion** in the sense that we can calculate the cardinality of the output from the cardinality of the inputs as

$$|A \cup B| = |A| + |B| - |A \cap B|.$$

This property is intuitively obvious since those elements in both A and B will be counted twice and hence need subtraction via the last term. We can even check it: in our example above |A| = 4 and |B| = 4. Checking our results we have that  $|A \cup B| = 6$  and  $|A \cap B| = 2$  and so by the principle of inclusion we should have 6 = 4 + 4 - 2 which makes sense.

### 1.2.3 Numeric Sets

Using this basic notation, we can define three important numeric sets which are used extensively later on in this chapter.

**Definition 13.** The **integers** are whole numbers which can be positive or negative and also include zero

$$\mathbb{Z} = \{\ldots, -3, -2, -1, 0, +1, +2, +3, \ldots\}.$$

The **natural numbers** are whole numbers which are positive

$$\mathbb{N} = \{0, 1, 2, 3, \ldots\}.$$

The **rational numbers** are those which can be expressed in the form p/q where p and q are integers called the **numerator** and **denominator**

$$\mathbb{Q} = \{ p/q : p \in \mathbb{Z} \land q \in \mathbb{Z} \land q \neq 0 \}.$$

Clearly the set of rational numbers is a super-set of both  $\mathbb{Z}$  and  $\mathbb{N}$  since, for example, we can write p/1 to represent any integer p as a member of  $\mathbb{Q}$ . However, not all numbers are rational. Some are **irrational** in the sense that it is impossible to find a p and q such that they exactly represent the required result; examples include the value of  $\pi$ .

### 1.2.4 Functions

**Definition 14.** If A and B are sets, a **function** f from A to B is a process that maps each element of A to an element of B. We write this as

$$f: A \rightarrow B$$

where A is termed the **domain** of f and B is the **codomain** of f. For an element  $x \in A$ , which we term the **preimage**, there is only one  $y = f(x) \in B$  which is termed the **image** of x. Finally, the set

1.2 Sets and Functions 15

$$\{y: y = f(x) \land x \in A \land y \in B\}$$

which is all possible results, is termed the **range** of f and is always a sub-set of the **codomain**.

As a concrete example, consider a function INV which takes an integer x as input and produces the rational number 1/x as output:

INV :

$$\mathbb{Z} \to \mathbb{Q}$$

, INV( $x$ ) =  $1/x$ .

Note that here we write the **function signature** which defines the domain and codomain of INV inline with the definition of the **function behaviour**. In this case the domain of INV is  $\mathbb{Z}$  since it takes integers as input; the codomain is  $\mathbb{Q}$  since it produces rational numbers as output. If we take an integer and apply the function to get something like INV(2) = 1/2, we have that 1/2 is the image of 2 or conversely 2 is the preimage of 1/2 under INV.

From this definition it might seem as though we can only have functions with one input and one output. However, remember that we are perfectly entitled to have sets of sets so we can easily define a function f, for example, as

$$f: A \times A \rightarrow B$$

.

This function takes elements from the Cartesian product of A as input and produces an element of B as output. So since pairs  $(x,y) \in A \times A$  are used as input, f can in some sense accept two input values. As a concrete example consider the function

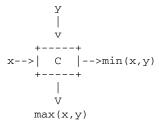

$$MAX : \mathbb{Z} \times \mathbb{Z} \to \mathbb{Z}, \quad MAX(x,y) = \begin{cases} x & \text{if } x > y \\ y & \text{otherwise.} \end{cases}$$

This is the maximum function on integers; it takes two integers as input and produces an integer, the maximum of the inputs, as output. So if we take a pair of integers, say (2,4), and apply the function we get Max(2,4)=4 where we usually omit the parentheses around the pair of inputs. In this case, the domain of Max is  $\mathbb{Z} \times \mathbb{Z}$  and the codomain is  $\mathbb{Z}$ ; the integer 4 is the image of the pair (2,4) under Max.

**Definition 15.** For a given function f, we say that f is

- **surjective** if the range equals the codomain, i.e., there are no elements in the codomain which do not have a preimage in the domain.

- **injective** if no two elements in the domain have the same image in the range.

- **bijective** if the function is both surjective and injective, i.e., every element in the domain is mapped to exactly one element in the codomain.

Using the examples above, we clearly have that INV is not surjective but MAX is. This follows because we can construct a rational 2/3 which does not have an integer preimage under INV so the function cannot be surjective. Equally, for any integer x in the range of MAX there is always a pair (x, y) in the domain such that x > y so

MAX is surjective, in fact there are lots of them since  $\mathbb{Z}$  is infinite in size! In the same way, we have that INV is injective but MAX is not. Only one preimage x maps to the value 1/x in the range under INV but there are multiple pairs (x,y) which map to the same image under MAX, for example 4 is the image of both (1,4) and (2,4) under MAX.

**Definition 16.** Given two functions  $f: A \to B$  and  $g: B \to C$ , the **composition** of f and g is denoted

$$g \circ f : A \rightarrow C$$

.

Given some input  $x \in A$ , this composition is equivalent to applying y = f(x) and then z = g(y) to get the result  $z \in C$ . More formally, we have

$$(g \circ f)(x) = g(f(x)).$$

The notation  $g \circ f$  should be read as "apply g to the result of applying f".

**Definition 17.** The **identity function**  $\mathscr{I}$  on a set A is defined by

$$\mathscr{I}: A \to A, \ \mathscr{I}(x) = x$$

so that it maps all elements to themselves. Given two functions f and g defined by  $f: A \to B$  and  $g: B \to A$ , if  $g \circ f$  is the identity function on set A and  $f \circ g$  is the identity on set B, then f is the **inverse** of g and g is the inverse of f. We denote this by  $f = g^{-1}$  and  $g = f^{-1}$ . If a function f has an inverse, we hence have  $f^{-1} \circ f = \mathscr{I}$ .

The inverse of a function maps elements from the codomain back into the domain, essentially reversing the original function. It is easy to see not all functions have an inverse. For example, if the function is not injective then there will be more than one potential preimage for the inverse of any image.

At first glance, it might seem like our example functions both have inverses but they do not. For example, given some value 1/x, we can certainly find x but we have already said that numbers like 2/3 also exist in the codomain so we cannot invert all the values we might come across. However, consider the example of a successor function on integers

$$SUCC: \mathbb{Z} \to \mathbb{Z}, SUCC(x) = x + 1$$

which takes an integer x as input and produces x+1 as output. The function is bijective since the codomain and range are the same and no two integers have the same successor. Thus we have an inverse and it is easy to describe as

$$PRED : \mathbb{Z} \to \mathbb{Z}, PRED(x) = x - 1$$

which is the predecessor function: it takes an integer x as input and produces x-1 as output. To see that  $SUCC^{-1} = PRED$  and  $SUCC^{-1} = PRED$  note that

$$(PRED \circ SUCC)(x) = (x+1) - 1 = x$$

1.2 Sets and Functions 17

which is the identity function. Conversely,

$$(SUCC \circ PRED)(x) = (x-1) + 1 = x$$

which is also the identity function.

### 1.2.5 Relations

**Definition 18.** We call a sequence of n elements  $(x_0, x_1, ..., x_{n-1})$  an n-tuple or simply a **tuple** when the number of elements is irrelevant. In the specific case of n = 2, we call  $(x_0, x_1)$  a **pair**. The i-th element of the tuple x is denoted  $x_i$ , and the number of elements in a particular tuple x may be written as |x|.

**Definition 19.** The Cartesian product of *n* sets, say  $A_0, A_1, \dots, A_{n-1}$ , is defined as

$$A_0 \times A_1 \times \cdots \times A_{n-1} = \{(a_0, a_1, \dots, a_{n-1}) : a_0 \in A_0, a_1 \in A_1, \dots, a_{n-1} \in A_{n-1}\}.$$

In the most simple case of n = 2, the Cartesian product  $A_0 \times A_1$  is the set of all possible pairs where the first item in the pair is a member of  $A_0$  and the second item is a member of  $A_1$ .

The Cartesian product of a set A with itself n times is denoted  $A^n$ . To be complete, we define  $A^0 = \emptyset$  and  $A^1 = A$ . Finally, by writing  $A^*$  we mean the Cartesian product of A with itself a finite number of times.

Cartesian products are useful to us since they allow easy description of sequences, or **vectors**, of elements. Firstly, we often use them to describe vectors of elements from a set. So for example, say we have the set of digits  $A = \{0, 1\}$ . The Cartesian product of A with itself is

$$A \times A = \{(0,0), (0,1), (1,0), (1,1)\}.$$

If you think of the pairs as more generally being vectors of these digits, the Cartesian product  $A^n$  is the set of all possible vectors of 0 and 1 which are n elements long.

**Definition 20.** Informally, a **binary relation** f on a set A is like a predicate function which takes members of the set as input and "filters" them to produce an output. As a result, for a set A the relation f forms a sub-set of  $A \times A$ . For a given set A and a binary relation f, we say f is

- **reflexive** if  $f(x,x) = \text{true for all } x \in A$ .

- **symmetric** if f(x,y) = true implies f(y,x) = true for all  $x,y \in A$ .

- **transitive** if f(x,y) = true and f(y,z) = true implies f(x,z) = true for all  $x,y,z \in A$ .

If f is reflexive, symmetric and transitive, then we call it an **equivalence relation**.

The easiest way to think about this is to consider a concrete example such as the case where our set is  $A = \{1, 2, 3, 4\}$  such that the Cartesian product is

$$A \times A = \left\{ \begin{aligned} &(1,1), \, (1,2), \, (1,3), \, (1,4), \\ &(2,1), \, (2,2), \, (2,3), \, (2,4), \\ &(3,1), \, (3,2), \, (3,3), \, (3,4), \\ &(4,1), \, (4,2), \, (4,3), \, (4,4) \end{aligned} \right\}.$$

Imagine we define a function

$$EQU: \mathbb{Z} \times \mathbb{Z} \to \{true, false\}, EQU(x, y) = \begin{cases} true & \text{if } x = y \\ false & \text{otherwise} \end{cases}$$

which tests whether two inputs are equal. Using the function we can form a sub-set of  $A \times A$  (called  $A_{\text{EOU}}$  for example) in the sense that we can pick out the pairs (x, y)

$$A_{\text{EOU}} = \{(1,1), (2,2), (3,3), (4,4)\}$$

where EQU(x,y) = true. For members of A, say  $x,y,z \in A$ , we have that EQU(x,x) = true so the relation is reflexive. If EQU(x,y) = true, then EQU(y,x) = true so the relation is also symmetric. Finally, if EQU(x,y) = true and EQU(y,z) = true, then we must have that EQU(x,z) = true so the relation is also transitive and hence an equivalence relation.

Now imagine we define another function

$$\operatorname{LTH}: \mathbb{Z} \times \mathbb{Z} \to \{\operatorname{true}, \operatorname{false}\}, \operatorname{LTH}(x,y) = \left\{ \begin{array}{ll} \operatorname{true} & \text{if} \quad x < y \\ \operatorname{false} & \text{otherwise} \end{array} \right.$$

which tests whether one input is less than another, and consider the sub-set of A

$$A_{I,TH} = \{(1,2), (1,3), (1,4), (2,3), (2,4), (3,4)\}$$

of all pairs (x,y) with  $x,y \in A$  such that LTH(x,y) = true. It cannot be that LTH(x,x) = true, so the relation is not reflexive; we say it is irreflexive. It also cannot be that if LTH(x,y) = true then LTH(y,x) = true, so the relation is also not symmetric; it is anti-symmetric. However, if both LTH(x,y) = true and LTH(y,z) = true, then LTH(x,z) = true so the relation is transitive.

## 1.3 Boolean Algebra

Most people are taught about simple numeric algebra in school. One has

- a set of values, say  $\mathbb{Z}$ ,

- a list of operations, say -, + and  $\cdot$ ,

- and a list of axioms which dictate how -, + and  $\cdot$  work.

1.3 Boolean Algebra 19

You might not know the names for these axioms but you probably know *how* they work, for example you probably know for some  $x, y, z \in \mathbb{Z}$  that x + (y + z) = (x + y) + z.

In the early 1840s, mathematician George Boole combined propositional logic and set theory to form a system which we now call Boolean algebra [4]. Put (rather too) simply, Boole saw that working with a logic expression *x* is much the same as working with a number *y*. One has

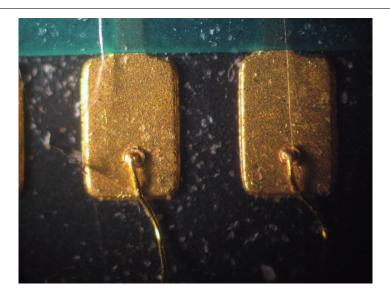

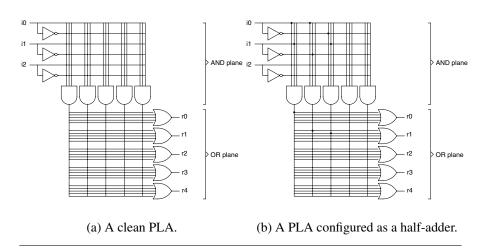

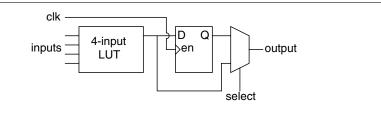

- a set of values, {false, true},